SASE 2017

El Simposio Argentino de Sistemas Embebidos, SASE2017, se realizó en la Facultad de Ingeniería de la Universidad de Buenos Aires, Argentina, del 9 al 11 de agosto 2017. Descargar Programa y Resúmenes. En el mismo se realizaron las siguientes actividades:

Workshops

Talleres en la modalidad hands-on.

Ing. Leandro Lanzieri (UTN FRA), Ing. E. Pernía (EXO/UNQ)

El objetivo de este workshop es introducir a personas sin experiencia en programación al mundo de los sistemas embebidos utilizando la nueva plataforma CIAA-BOT. Mediante el uso del software de programación gráfica de bloques encastrables (estilo Scratch/Snap) se programará la plataforma EDU-CIAA-NXP (la versión educativa de la CIAA-NXP) junto a unas maquetas electrónicas de forna sencilla, didáctica y entretenida. Ideal para personas sin experiencia previa o docentes que quieren introducir a alumnos de secundaria a la programación. Más información en: https://leandrolanzieri.github.io/ciaabot-ide/.

IMartin Ribelotta (Emtech)

Durante este workshop haremos una breve introducción a MicroPython, explicaremos como grabar el firmware de MicroPython en una EDU-CIAA, daremos una breve introducción al lenguaje Pytnon y programaremos la CIAA mediante ejemplos variados que cubren temas simples de programación básica, y temas más complejos que implican el uso avanzado del hardware que posee la placa.

Ing. Eric Pernía (EXO/UNQ), Dr. Lic. Carlos Lombardi (UNQ)

En este workshop se introduce la programación de PLCs (Controlador lógico Programable) en lenguaje Ladder Diagram utilizando el software IDE4PLC del Proyecto CIAA. Se realizarán durante el mismo programas típicos de aplicación en automatización industrial.

Ing. Diego Brengi (INTI, UNLaM), Ing. Gonzalo Cuenca (UNER)

Presentación del software KiCad, sus partes principales y descripción de las herramientas de diseño de circuitos esquemáticos, diseño de circuitos impresos (ruteo de PCBs) y modelización 3D de la placa. Con la ayuda de un ejercicio basado en un Poncho para la EDU-CIAA se desarrolla el método de trabajo para diseñar un PCB.

Ing. Eric Pernía (EXO/UNQ)

Se presenta en el Workshop la biblioteca oficial de las plataformas CIAA, llamada sAPI, mediante la práctica con ejemplos utilizando múltiples periféricos, entre ellos, GPIO, ADC, DAC, I2C, SPI. Se espera que al finalizar el mismo los asistentes sean capaces de realizar sus propios proyectos con la CIAA en lenguaje C, manejando una amplia gama de periféricos.

Ing. N. Gonzalez, L. Sugezky (UTN-FRBA)

El uso de modelos para describir el software en sistemas embebidos es cada vez más frecuente. uModel Factory es un software nacido en el seno de la UTN-FRBA de distribución libre que permite la creación y simulación de modelos, como así también su representación en lenguaje C posibilitando su uso en el ámbito académico y profesional.

Ing. Esteban Volentini (UNT)

Introducción al mundo del testing. ¿Se puede testear primero y programar después? Temas a tratar: Conceptos generales de Testing. Herramientas para facilitar el testing: Unity para verificar las condiciones, CMock y FakeFunctionFramework para emular funciones, Ceddling para gestionar el proyecto. Repositorios y Continuos Integration.

Mg. Bing. Eduardo Filomena (UNER), Bing. Juan Manuel Reta (UNER)

Este workshop ofrece una formación en la implementación de aplicaciones sencillas sobre la plataforma EDU-CIAA empleando lenguaje C. Además, proporciona las herramientas necesarias para desarrollar aplicaciones en distintos escenarios profesionales. Se remarca la importancia del uso de capas de abstracción de hardware tales como la biblioteca de funciones LPCOpen y el desarrollo y manejo de drivers.

Ing. Dario Baliña (Vortex)

Modelado, codificación, ejecución y depuración de Statecharts utilizando el Framework RKH sobre EDU-CIAA. Se aplicarán los conceptos de la programación dirigida por eventos y el modelo de ejecución de objeto activo.

Ing. Facundo Larosa (UTN-FRH), Martín Fernández (UTN-FRH)

Este curso comprende la utilización del modelo multicore del LPC 4337 para la implementación de programas en ambos núcleos y su comunicación.

Ing. Diego Dujovne (UDP), Dr. Ing. Carlos Taffernaberry (UTN FRM)

«En este taller se analizará el uso y aplicación del stack IPv6 para aplicaciones de internet industrial de las cosas, a través del uso de la plataforma OpenWSN. Esta plataforma, escrita en C y Python, contiene un sistema operativo básico junto con una implementación del stack en código abierto, quepermite incorporar aplicaciones.

OpenWSN (www.openwsn.org) puede ejecutarse en modo simulación o como una suite de firmware con una red de nodos de hardware abierto OpenMote (www.openmote.com) mas una interfaz de usuario y debugging en software que corre en una terminal. Este stack está actualmente en un proceso de estandarización avanzado en la Internet Engineering Task Force (IETF), dentro del grupo de trabajo 6tisch, cuyas normas se publican en forma de Request For Comments (o RFCs).

Dr. Ing. José Urriza (UNPSJB)

Introducción a los Sistemas de Tiempo Real (STR). Disciplinas de prioridades. Inversión de prioridad. Protocolos de Herencia de Prioridades y Techo. Evaluación de planificabilidad mediante métodos por cotas y exactos. Introducción a los STR Heterogéneos. Métodos de administración de tiempo ocioso en un STR para planificación heterogéneas: Servidores (Background, Polling y Deferrable), Dual Priority y Slack Stealing. Conceptos de Sistemas Operativos de Tiempo Real (SOTR). Implementación de un STR con FreeRTOS. Planificación de tareas mixtas mediante una Tarea Planificadora Heterogénea y/o modificaciones al planificador del SOTR. Arquitectura de las placas de desarrollo a emplear en el curso, y sus ambientes de desarrollo y librerías. Sistemas Embebidos y de Tiempo Real.

Ing. Esteban Volentini (UNT), Ing. Gustavo Muro (UNR)

El objetivo del workshop es hacer un breve repaso sobre las características de un OSEK como Sistema Operativo de Tiempo Real y una introducción a la estructura del Firmware de la CIAA, desarrollando ejemplos sencillos para familiarizarse con el desarrollo de aplicaciones que utilicen el conjunto de OSEK y POSIX del CIAA Firmware.

Ing. Andrés Miguel Airabella. (Satellogic S.A./UNSL)

El objetivo es aprender a describir un sistema digital en VHDL, e implementarlo en un FPGA. Se usarán kits de desarrollo para realizar distintos laboratorios luego de aprender la sintaxis básica de síntesis en VHDL. Contenido: FPGA: Descripción. Clasificación. Arquitectura. Bases del VHDL. Formato. Librerías estandarizadas. Tipos de datos. Declaraciones concurrentes. Declaraciones secuenciales. Funciones de conversión. Librerías opensource, librerías pagas, librerías definidas por el usuario. Uso de librerías mediante componentes. Sistemas de desarrollo. Para la parte práctica del curso se usarán las plataformas de Altera FPGA Board EP2C8Q208 y EP4CE6E22C8.

Carlos Pantelides (ACSE)

El objetivo de la actividad es implantar el modelo mental unix y de interacción mediante la linea de comandos con una computadora mientras se transmiten algunos conocimientos básicos y ejemplos concretos de uso.

En una primera parte se ejercitará la puesta en marcha de una máquina virtual mientras se explican la teoría e historia. Luego, de modo práctico e iterativo se verán los comandos más útiles y como se relacionan. La práctica es casi permanente, regada de truquitos y completamente abierta y adaptable a la situación de las personas asistentes.

Ing. Ezequiel Espósito, MBA Lic. Joaquin Zoilo, Ing. Diego Fernandez (Debmedia)

Se trata de un workshop orientado a herramientas y técnicas modernas que permiten transformar una idea tecnológica en una startup exitosa. El taller está orientado a conocer, mediante ejemplos prácticos, las buenas prácticas que utilizan las empresas alrededor del mundo para alcanzar el éxito. El taller va a estar divido en cinco etapas, las mismas etapas por las que pasan todas las empresas: creación, validación, calibración, expansión y profesionalización. Entre otros temas, hablaremos sobre Análisis de Mercado, Lean Startup, Modelos de Negocios Tecnológicos, Financiamiento, etc.

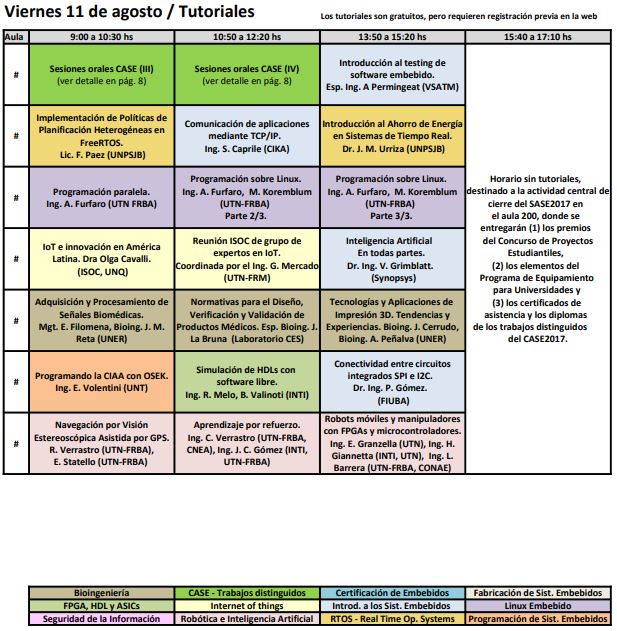

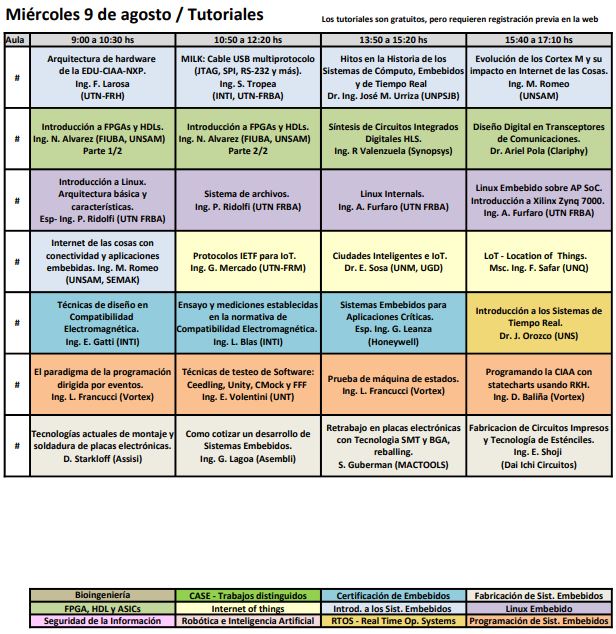

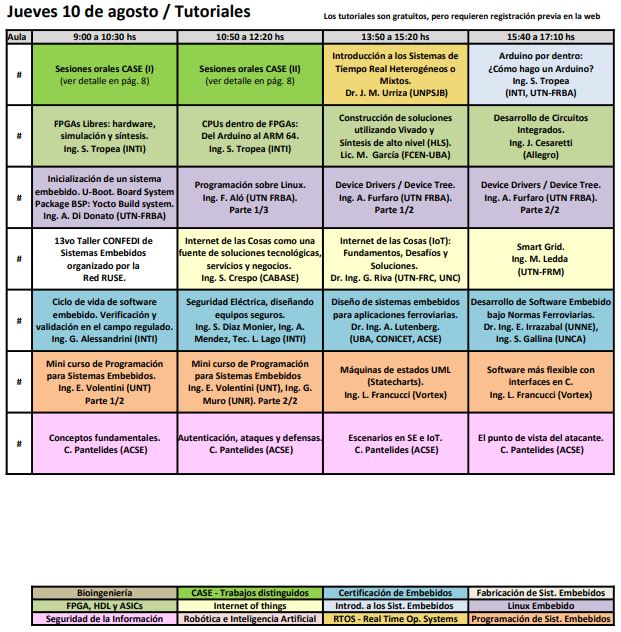

Tutoriales

Charlas técnicas de 90 minutos de duración, agrupadas por temas.

Ing. Facundo Larosa (UTN-FRH)

Presentación del diseño de hardware de la EduCIAA NXP. Arquitectura del microcontrolador LPC4337 (basado en Cortex M4F). Características principales. Comparación con otros dispositivos de la misma y otras familias.

Ing. Marcelo Romeo (UNSAM, SEMAK)

En los últimos años se ha expandido explosivamente las conexiones inalámbricas entre dispositivos embebidos. Desde hace algún tiempo se ha aprovechado la instalación de telefonía celular para implementar conectividad GPRS. Recientemente han aparecido otras metodologías de comunicación que permiten transmitir información a grans distancia con bajísimo consumo. Se conoce como LoRa. En esta presentación introduciremos módulos GPRS y LoRa con microcontroladores incorporados y con técnicas de desarrollo y depuración estándares (MBED) y analizaremos ejemplos de aplicación en Internet de las Cosas.

Ing. Salvador Tropea (INTI, UTN-FRBA)

Para programar y/o depurar microcontroladores frecuentemente utilizamos un «cable». Lo mismo sucede a la hora de configurar FPGAs o grabar memorias serie. Por «cable» normalmente se entiende un circuito que conectamos a la PC y que nos permite realizar las tareas antes mencionadas. En las tareas cotidianas de nuestro laboratorio frecuentemente programamos microcontroladores AVR y ARM, así como también configuramos FPGAs de Xilinx y Lattice. Cada familia de dispositivos utiliza un «»cable»» diferente. MILK es una solución que permite realizar todas estas tareas con un único cable. Su diseño es abierto y basado en un esquema de plug-ins.

Dr. Ing. José M. Urriza (UNPSJB)

Una breve revisión de los primeros sistemas de cómputo electrónicos, aplicados a computación general, embebida o de aplicaciones de tiempo real hasta los desarrollos de las últimas décadas.

Ing. Marcelo Romeo (UNSAM, UTN-FRBA)

A los tradicionales Cortex M0, M3 y M4, en los últimos años se agregó Cortex M7 que incorpora memorias cache, corrección de errores en datos, mejora el procesamiento de punto flotante y se presenta como una opción introductoria del mundo de los sistemas embebidos fuertemente determinísticos al explosivo mundo de internet de las cosas.

También la aparición de las versión de la arquitectura V8 dio lugar a las familias M23 y M33. En esta presentación haremos un recorrido sobre las novedades de las familias y nos detendremos en ejemplos de aplicación.

Ing. Salvador Tropea (INTI, UTN-FRBA)

En esta charla veremos que es lo que implica que un dispositivo sea compatible con Arduino. Se expondrán requisitos físicos, mecanismos de comunicación, estructura de la API e integración con la IDE de Arduino. Los temas serán expuestos a partir de la experiencia de implementar una placa compatible con Arduino UNO r3 utilizando una FPGA.

Ing. Sergio Caprile (CIKA)

Análisis de las tribulaciones y lamentos (a modo preemptive) con que se encuentra el desarrollador no asociado a una empresa multinacional a la hora de realizar un desarrollo de un sistema dedicado con comunicación TCP/IP utilizando (Fast) Ethernet y/o Wi-Fi.

Ing. Alejandro Permingeat (VSAT Motion)

El protagonismo que esta tomando el software en los sistemas embebidos trae aparejado no solo beneficios sino también mayores exigencias. Esta mayor participación del software muchas veces implica que fallas en el software tengan un mayor impacto. Por lo tanto conocer las debilidades y los riesgos del software es de vital importancia. Este es el objetivo central de las tareas del testing de software.

Ing. Victor Grimblatt (Synopsys)

El año pasado el programa computacional AlphaGo venció al dan 9 y 18 veces campeón mundial de Go Lee-Se-dol por 4 a 1. Este año, en Barcelona, el fundador y CEO de SoftBank, Masayashi Son, predijo que en el 2045 los computadores hechos con chips integrando 3 cuatrillones (3 x 10^12) de transistores, tendrán un coeficiente intelectual de 10.000. La inteligencia artificial está cambiando las reglas del juego y generando nuevos desafíos para el desarrollo de sistemas electrónicos. En este tutorial analizaremos estos nuevos desafíos a partir de 5 perspectivas: Ley de Moore, verificación continua, uso de propiedad intelectual (IP), más allá de la ley de Moore, y calidad, integridad y seguridad del software.

Dr. Ing. Pablo Gomez (FIUBA)

SPI: Características generales y dispositivos que lo utilizan. Topologías con esclavos múltiples. Polaridad y fase del reloj. Ventajas y desventajas de su uso. I2C: Descripción general, aplicaciones. Comparación con otros protocolos. Arquitectura del hardware. Direccionamiento. Arbitraje. Ejemplo de un multiplexor I2C PCA9548. Ejemplo práctico con un expansor de puertos (PCA9532).

Ing. Leandro Francucci (Vortex)

Presentación de los fundamentos del paradigma de la programación reactiva o dirigida por eventos, utilizando máquinas de estados Statecharts en ejecución simultanea, el patrón de objetos activos para la programación concurrente, comparando este último con la ejecución cíclica o super-loop y los OS/RTOS, eventos sincrónicos y asincrónicos, colas de eventos, lazo de eventos o planificador reactivo en sus modos preemptive y cooperative, aplicación en sistemas bare-metal y con OS/RTOS. Finalmente, para llevar estos conceptos de manera rápida y simple a la práctica, se presentarán diferentes paquetes de software (específicamente frameworks) y herramientas que ofrece el mercado actual.

Ing. Esteban Volentini (UNT)

Introducción al mundo del testing. ¿Se puede testear primero y programar después? Temas a tratar: Conceptos generales de Testing. Herramientas para facilitar el testing: Unity para verificar las condiciones, CMock y FakeFunctionFramework para emular funciones, Ceddling para gestionar el proyecto. Repositorios y Continuos Integration.

Ing. Leandro Francucci (Vortex)

Presentación de estrategias, como punto de partida, para probar software que representa máquinas de estados tanto tradicionales (o planas) como de estados anidados (o jerárquicas). Aplicando conceptos como el desacople de módulos, el uso de stub, spy y mock, casos de prueba unitarios y sus fases, entre otros. Cada una de las estrategias expuestas se respalda con ejemplos de código fuente, escritos en lenguaje C para el framework de prueba Unity y Cmock. Finalmente, se presenta una estrategia para probar máquinas de estados anidados, resuelta por el framework RKH, el cual permite representar máquinas de estados y objetos activos concurrentes en lenguaje C/C++.

Ing. Dario Baliña (Vortex)

Guía para el desarrollo de aplicaciones con statecharts. Detalle de servicios que provee y su configuración. Funcionamiento baremetal y en conjunto con RTOS.

Ing. Esteban Volentini (UNT), Ing. Gustavo Muro (UNR).

Técnicas profesionales para el desarrollo de Firmware. Comenzando por las buenas prácticas en la arquitectura y la programación, pasando por procesos de desarrollo, modalidades de testeo y finalizando con metodologías de automatización. Temas a tratar: Arquitectura de programas portables. Estructura de Includes. Calidad. Ejemplos de Programación. Testeo estático y dinámico. Procesos de desarrollo. Técnicas y herramientas para hacer esto posible: Gerrit y Continuos Integration.

Ing. Leandro Francucci (Vortex).

Presentación de la especificación (semántica y notación) de las máquinas de estados UML, las cuales se basan en Statecharts, con el objectivo de difundirla de una manera más clara y comprensible. Fomentando así, la estandarización y uniformidad de estos conceptos, evitando depender de la semántica y notación particular que difunden diferentes autores, profesionales y proveedores dedicados al modelado de software, en especial para el segmento de los embedded systems. Promoviendo, de esta manera, un lenguaje común para aquellos que trabajan con modelos de comportamiento dinámico de software, especialmente máquinas de estados aplicadas al desarrollo de embedded software, las cuales representan la dinámica de la totalidad o parte de un sistema.

Ing. Leandro Francucci (Vortex).

Presentación de abstracciones de software aplicadas en lenguaje C, para lograr un software más flexible, reutilizable, transportable, legible, fácil de probar y mantener, promoviendo lo que se conoce como código limpio y el diseño ágil de software. El objetivo es comprender la utilización de abstracciones, mediante la herencia y el polimorfismo en lenguaje C. ¿Porqué y cuándo aplicarlas?. Definición y aplicación de interfaces y operaciones polimórficas. Selección de implementación de interfaces en tiempo de compilación y en tiempo de ejecución. Estos conceptos se respaldan con estrategias de programación en C para lograr su implementación inmediata!

Ing. Esteban Volentini (UNT).

Introducción a OSEK-OS, un Sistema Operativo Estático para Sistemas Embebidos de Tiempo Real. OSEK-OS es utilizado ampliamente en los controladores de la industria automotriz. Los ejemplos de este tutorial se basan en el CIAA-Firmware.

Esp. Ing. Pablo Ridolfi (UTN-FRBA).

Linux se ha transformado en un sistema operativo de amplia aplicación, tanto para sistemas de propósito general como Real Time, pudiendo hostearse en clusters de alto rendimiento, servers, computadores de escritorio, y hasta en sistemas embebidos de prestaciones mínimas. En el mercado de dispositivos móviles una variante de este popular sistema operativo, Android, ha terminado desplazando las versiones mobile de Windows que no logran mas de un 4% del share de sistemas operativos en el mercado de smartphnoes. Debido a su creciente aplicación en el área de embedded es necesario comenzar a considerarlo máxime teniendo en cuenta que de acuerdo a la vertiginosa evolución de las tecnologías de integración es de esperar que en algunos pocos años por un dolar se pueda fabricar en escala, cualquier procesador pueda tener los recursos mínimos necesarios para hostear linux de manera adecuada, desplazando a otras soluciones que no respetan estándares ni tienen el nivel de soporte que Linux ha desarrollado a través de su cada vez. El presente Tutorial dará una introducción a sus características principales y a su arquitectura básica.

Esp. Ing. Pablo Ridolfi (UTN-FRBA).

En los sistemas computacionales relativamente complejos se presenta la necesidad de almacenar diferentes tipo datos en los más diversos medios de almacenamiento. Esta funcionalidad debe ser resuelta de forma transparente al desarrollador de software de medio y alto nivel. A fin de satisfacer este requerimiento se han implementado una gran variedad de sistemas de archivos. Este seminario tiene por objeto brindar los conceptos básicos asociados a cualquier sistema de archivos, así como también mostrar las diferencias entre los tipos más reconocidos analizando sus características según el medio y la misión para el cual se utilicen.

Ing. Alejandro Furfaro (UTN-FRBA)

En especial al construir la imagen de memoria de un sistema embebido es necesario conocer donde se inserta el Sistema Operativo y conocer su funcionamiento interno de modo de mejorar las posibilidades e ideas que surgen al trabajar tanto en su construcción como en el desarrollo de aplicaciones. Este tutorial abordará aspectos internos de la arquitectura, arranque inicialización y estructuras fundamentales para gestión de procesos y manejo de la memoria y las interrupciones.

Ing. Alejandro Furfaro (UTN-FRBA)

Los dispositivos lógicos programables han evolucionado hacia un paradigma en el que combinan celdas programables con cores de procesamiento ARM (AP SoC: All Programmable SoC), esto permite disponer en un mismo sistema recursos de lógica programable con cores de procesamiento capaces de ejecutar Linux como sistema operativo en forma completa. Ambos sistemas pueden trabajar en forma independiente o en conjunto, permitiendo desarrollar hardware programable dentro del mismo sistema de desarrollo e integrar la solución de hardware directamente a los Cores. En este tutorial se dará una introducción a Zynq 7000 de Xilinx el cual combina dos cores CORTEX A9 con recursos de hardware suficientes para poder bootear en forma directa un sistema operativo Linux. El objetivo de este tutorial es describir las principales características de este sistema y exponer como instalar un sistema operativo Linux.

Ing. Andrés Di Donato (UTN-FRBA).

En la actualidad diversos sistemas embebidos de mediana y gran capacidad de procesamiento requieren un sistema operativo que administre todos los recursos de hardware disponibles. La gran mayoría de ellos utiliza Linux como SO encargado de administrar dichos recursos. Éste SO requiere una configuración especifica para cada procesador y board disponibles en el mercado. Por lo tanto el armado de una imagen del Sistema Operativo a medida de nuestro Sistema de Hardware (Procesador, periféricos, controlador de memoria, y cualquier otro componente de hardware, que le permita bootear el sistema, y operar de acerdo a lo requerido (u-boot, Kernel, rootfs y device tree) es una tarea compleja y de baja repetibilidad. Por esto se han desarrollado los BSPs que facilitan la creación y customización de imágenes de Linux Embebido. En este tutorial se verán los fundamentos de Buildroot / openembedded y Yocto. Se explorarán las ventajas y desventajas de cada uno de ellos.

Ing. Fernando Aló UTN-FRBA).

El estandar POSIX (de Portable Operating System based on unIX) lleva mas de 40 años de aplicación en el mundo de los sistemas operativos. Al tratarse de un estándar abierto se ha adoptado en la totalidad de los sistemas operativos conocidos como UNIX-like, y ha terminado por ponerse en otras implementaciones de sistemas operativos Real time comerciales como QNX. Es uno de los paradigmas de portabilidad de código lo cual implica la reusabilidad de aplicaciones en cualquier plataforma con una simple

recompilación. Este tutorial dará una introducción al estándar POSIX sus funciones y la simplificación que supone para el acceso a la entrada salida. Se comprobará el uso de aplicaciones en plataformas heterogéneas reduciéndose el time to market al usar la misma aplicación en cada componente de un sistema distribuido. La segunda parte del Tutorial boaradrá los promeros ejemplos prácticos de programación sobre plataformas heterogéneas mostrando la portabilidad de código, con solo recompilar las aplicaciones. Se realizarán aplicaciones con crosscompilación para acceso a la entrada salida mediante simples funciones basadas en el paradigma everything is a file. Poro otra parte se aplicarán las funciones básicas para creación y control de procesos, redirección de entrada salida a flujos asimilando su operación al manejo de archivos.

Ing. Alejandro Furfaro (UTN-FRBA).

Actualmente existen diversas soluciones de hardware, las cuales pueden ser aplicadas a una gran variedad de aplicaciones. Muchos de estos sistemas embebidos tienen algo en común, el sistema operativo Linux como administrador de recursos. A la hora de poner a prueba el hardware con todos sus periféricos y funcionalidades, a la hora de comunicar el mismo con otros dispositivos, necesitamos conocer la política de gestión de estos recursos por parte del SO. Por esto, este seminario tiene como objetivo dar una breve introducción al manejo de drivers en Linux / Android embebido, Device tree, con ejemplos y metodologías sencillas.

Ing. Alejandro Furfaro (UTN-FRBA).

A medida que progresa le scaling de dispositivos se consigue integrar mayor cantidad de componentes dentro de un mismo chip, llegándose de este modo a la meta de integrar varios cores de procesamiento, al principio en procesadores para equipos de alto rendimiento y actualmente en cualquier smartphone avanzado. Saber como aprovechar las ventajas de disponer de múltiples cores de procesamiento en un mismo sistema.tanto en las aplicaciones como en el funcionamiento del scheduler del sistema operativo, en ocasiones hace la diferencia. El presente tutorial abordará los rudimeintos de hardware de procesamiento paralelo y técnicas de programación que aprovechen estas prestaciones.

Ing. Alejandro Furfaro y Sr. Mariano Koremblum (UTN-FRBA).

En este tutorial se mostrará el desarrollo de aplicaciones capaces de crear procesos y controlar su ejecución desde un proceso principal. Se abordarán los mecanismos mas rudimentarios de comunicación mediante señales y pipes, redirección de E/S, concurrencia y manejo de comunicación por red de datos, y control adecuado de finalización de los procesos. Luego de este tutorial se habrá visto el desarrollo de un servidor concurrente que maneje conexiones por TCP y transferencias por UDP, resolviendo la gestión de los procesos hijos del servidor.

Ing. Alejandro Furfaro y Sr. Mariano Koremblum (UTN-FRBA).

La versión de UNIX conocida como System V marcó un hito fundamental en la evolución de los Sistemas Operativos POSIX. No solo por basarse en ese standard sino por muchas nuevas y poderosas funciones. Los mecanismos de intercomunicación de procesos conocidos como System V IPCs son una de ellas. El presente Tutorial aborda los mecanismos de Intercmunicación de procesos System V: Colas de Mensajes, Semáforos, y Shared Memory. Su modelo de programación y su estructura interna. En el Tutorial se muestra su implementación integrándolos al servidor concurrente del Tutorial 10.

Dante Starkloff (Assisi, CADIPEL)

Historia y desarrollo de las tecnologías del montaje y soldadura derivadas de los avances en la miniaturización de los componentes. Desde la válvulas hasta hoy. Componentes THT y SMT – Inserción manual y Pick and Place – Soldadura manual, por ola y por reflow – Controles visuales versus AOI – Tips para diseños correctos de circuitos impresos.

Ing. Gastón Lagoa (Asembli SA)

Características para el diseño de Sistemas embebidos desde el diseño hasta la comercialización. Gestión del proyecto, Oferta, Propuesta, Mercado, Plan de Marketing, Capitalización.

Sergio Guberman (MACTOOLS SA)

Componentes SMD – Clasificacion – Medidas – Formatos de pines – Tarjetas – Revestimiento – Metodos de soldadura y desoldadura – Equipamiento – Estaños – Temperaturas – Flux. Tipos, consideraciones y clasificación de componentes BGA – Metodos de Remocion, Instalacion e inspección – Fijacion de perfiles – Equipos Infra Rojos, media y alta gama –Reballing.

Ing. Enrique Shoji (Dai Ichi Circuitos S.A.)

Cómo tener en cuenta los lineamientos para poder resolver los diseños de los circuitos impresos, con referencia a la manufactura, montaje y amigable con el ambiente.

Ing. Gustavo Mercado (UTN-FRM)

El Internet Engineering Task Force (IETF) es una de las más importantes entidades de estandarización de los protocolos de Internet. Como tal y desde hace unos años, ha venido generando varios protocolos para la nueva forma de conectar objetos, que genéricamente se conoce con Internet of Things. En este tutorial se revisan estos nuevos protocolos como así también los grupos de trabajo donde fueron creados. Los protocolos mostrados son: 6lowPAN, 6TiSCH, RPL, ACE y CoAP.

Dr. Eduardo Sosa (UNM, UGD)

La importancia cada vez mayor en la sociedad de IoT está relacionada con su capacidad de conectar a las personas, los bienes y las operaciones a través de una red global, lo que permite una mayor competitividad de las empresas globales que comparten un conocimiento específico y el valor social a través del tiempo. Los avances en computación ubicua facilitan el desarrollo de aplicaciones que son consideradas parte esencial de la denominada Internet del Futuro, de los Ambientes Inteligentes y por ende las Ciudades Inteligentes. Hacer a una ciudad «inteligente» está emergiendo como una estrategia para mitigar los problemas generados por el crecimiento de la población urbana y la consecuente rápida urbanización. Este segmento del evento presenta un marco tendiente a esclarecer el concepto de ciudades inteligentes, identificando las áreas críticas de las iniciativas inteligentes de gestión de la ciudad.

MSc. Ing. Félix Safar (UNQ).

La temática de LoT (Location of Things) es un eje central de IoT para la vinculación entre el mundo físico y el cibernético. En este tutorial se cubren tanto técnicas para posicionamiento Outdoor (GPS y GPS-RTK) como Indoor (WiFi, Beacons, Ultrasonido, UWB) evaluando sus características de precisión y exactitud, modelos de cálculo de posición, ventajas, desventajas, fusión con otros sensores inerciales y post procesamiento de Kalman para mejorar la calidad de las estimaciones. Se dan a conocer ejemplos y casos de aplicación.

Ing. Salvador Crespo (CABASE).

Actual infraestructura de redes de prestadores con antiguos modelos de negocio, migrando hacia innovadoras soluciones y servicios basado en IoT que generan nuevas oportunidades de negocios escalables.

Dr. Ing. Guillermo Riva (UTN-FRC, UNC).

La conferencia se enfoca en describir el concepto de IoT y sus alcances. Se presentan las tecnologías generales que habilitan este paradigma. Se describen en detalle las tecnologías de comunicaciones para IoT tradicionales y las surgidas recientemente (IEEE 802.11ah, IEEE 802.11af, NB-IoT, LORA, Sigfox, Weightless, Ingenu, Thread, etc). Se presentan las principales limitaciones actuales para el despliegue masivo de IoT, y se plantean potenciales soluciones y líneas de trabajo futuras.

Ing. Marcelo Ledda (UTN-FRM).

Desde un contexto global, la red eléctrica inteligente (smart grid en inglés) se puede definir como la integración dinámica de los desarrollos en ingeniería eléctrica y los avances de las tecnologías de la información y comunicación (o TIC), dentro del negocio de la energía eléctrica (generación, transmisión, distribución y comercialización, incluyendo las energías alternativas); permitiendo que las áreas de coordinación de protecciones, control, instrumentación, medida, calidad y administración de energía, etc., sean concatenadas en un solo sistema de gestión con el objetivo primordial de realizar un uso eficiente y racional de la energía.En el tutorial se describe el proyecto “Smart Grid San Martin – Red Eléctrica de Inteligente y con Generación Fotovoltaica Distribuida”. El proyecto es financiado por Mincyt FONARSEC UREE.

Dra. Olga Cavalli (ISOC Ar, UNQ).

El uso de la tecnología de IoT ha generado una serie de desarrollos innovadores en América Latina. Desde aplicaciones para mejorar ambientes de trabajo, cuidado del medioambiente o favorecer la agricultura, hasta misma la creación de plataformas para desarrollo de IoT. Esta presentación detalla una serie de proyectos innovadores desarrollados en América Latina los que han sido creados en base a IoT.

Coordinada por el Ing. G. Mercado (UTN-FRM)

Reunión de expertos en IoT – académicos, investigadores e industria – con el objetivo de pasar revista a las iniciativas, investigaciones y aplicaciones de IoT de la región y plantear un plan de acción para la promoción y fortalecimiento de las actividades de IoT.

Ing. Edmundo Gatti (INTI)

Se presentarán las reglas generales a tener en cuenta en el diseño de equipos electrónicos sensitivos, para alcanzar el cumplimiento de la normativa aplicable en Compatibilidad Electromagnética. Distintas técnicas de control de las interferencias electromagnéticas aplicadas en la puesta a tierra, en la configuración de masas, en el blindaje, supresión y filtrado y en el diseño de circuitos impresos.

Ing. Luciano Blas (INTI)

Se presentarán los conceptos generales y definiciones de la Compatibilidad Electromagnética entre equipos, sistemas y su entorno. Se presentará la normativa vigente tanto en el campo regulado como el voluntario y se describirán las técnicas de medición y ensayo aplicables para caracterizar tanto el perfil de emisión como de inmunidad de diferentes equipos y sistemas.

Esp. Ing. Guillermo Leanza (Honeywell, FIUBA)

Cuando diseñamos un sistema que cuando falla puede ocasionar, daño a las personas , al medio ambiente o también perdidas económicas importantes, nos encontramos con el caso de un sistema crítico.

En la actualidad los sistemas embebidos se utilizan en todo tipo de industrias, por ejemplo: procesos, aviación, automotriz, ferroviaria, etc. Para usar un sistema embebido en una aplicación crítica, debemos realizar el diseño de modo de asegurar que un posible fallo no produzca consecuencias indeseadas.

Existen técnicas, basadas en estándares internacionales, que nos ayudan como guía para el desarrollo del hardware y software a fin de lograr su funcionamiento sea el esperado.

Este tutorial, permite al asistente, tomar conocimiento de los desafíos al momento de plantear un desarrollo libre de fallas.

Ing. Gustavo Alessandrini (INTI)

Ciclo de vida. Verificación y Validación. Gestión de riesgo. Trazabilidad. Herramientas y procesos. Normativas.

Ing. S. Diaz Monier, Ing. A. Mendez, Tec. L. Lago (INTI)

¿Por qué diseñar con seguridad eléctrica? ¿Donde encontrar criterios Normativa. Requisitos y criterios para el diseño.

Dr. Ing. Ariel Lutenberg (FIUBA, CONICET, ACSE)

El mal diseño o implementación de un sistema ferroviario puede derivar en accidentes con cientos de victimas fatales y miles de heridos. En este tutorial se introducen los criterios y metodologías que se utilizan en los países con alto desarrollo tecnológico para desarrollar sistemas con la fiabilidad, disponibilidad, mantenibilidad y seguridad (RAMS) necesarias para aplicaciones con este nivel de criticidad. Los conceptos que se explicarán pueden ser adaptados y utilizados en otros campos de aplicación con niveles de criticidad similares.

Dr. Ing. Emanuel Irrazábal (UNNE), Ing. Sergio Gallina (UNCA)

Se presentan técnicas de desarrollo de sistemas electrónicos para aplicaciones ferroviarias críticas mediante el análisis de casos concretos, desde la normativa hasta el diseño e implementación del hardware, firmware y software. Se analiza el uso de buenas prácticas y herramientas con las cuáles se logra cumplir con las normas internacionales de seguridad y de calidad del proceso de desarrollo.

Dr. Ing. Javier D. Orozco (UNS)

Definiciones, clasificación, conceptos de planificación, técnicas de planificación con recursos compartidos y requerimientos heterogéneos, sincronización de procesos.

Dr. Ing. José M. Urriza (UNPSJB)

Principales métodos existentes en la teoría de Tiempo Real para convertir un Sistema Operativo de Tiempo Real en Heterogéneo.

Lic. F. Paez (UNPSJB)

En este tutorial se presenta la implementación de múltiples políticas de planificación heterogéneas sobre el SOTR FreeRTOS. Mediante estas políticas es posible planificar concurrentemente tareas críticas con tareas no-críticas y/o aperiódicas/esporádicas, sin comprometer el cumplimiento de las constricciones temporales de las primeras, y brindando una mejor calidad de servicio a las últimas.

Dr. José M. Urriza (UNPSJB)

Algunos métodos de la teoría de Tiempo Real para ahorro de energía en un Sistema Operativo de Tiempo Real.

Ing. N. Alvarez (FIUBA)

Descripción de las FPGAs. Conformación interna, tecnología. Uso en aplicaciones. Introducción a los HDLs. Introducción a VHDL. Elementos y estructura del lenguaje. Desarrollo de componentes digitales. Diseño de bancos de prueba básicos.

Ing. Ronald Valenzuela (Synopsys)

Predicho por Moore en 1965, la capacidad moderna de integración de los circuitos ha llegado a una escala que permite billones de transistores operando en sincronía. A esta escala, la enorme complejidad de los circuitos modernos sólo es posible debido a la automatización que, mediante Software, permite convertir una descripción textual de un circuito y convertirlo en una red de compuertas. La charla pretende hacer una revisión de las técnicas modernas que se ejecutan durante la síntesis lógica y física de estos circuitos, desde la perspectiva de los diseñadores. Se discutirán conceptos básicos, las optimizaciones, el manejo de interconexiones y la síntesis física.

Dr. Ing. Ariel Pola (Clariphy)

Como resultado del constante aumento del tráfico de información, en los últimos años la industria de las telecomunicaciones ha evolucionado de manera vertiginosa. Este hecho exige el diseño de nuevos transceptores de comunicaciones digitales que permitan aumentar la velocidad de procesamiento. Tal condición impone varios desafíos en las implementaciones de los sistemas de procesamiento digital de señales (DSP), las cuales debe satisfacer tanto las altas tasas de procesamiento, así como también la reducción de espacio y consumo de energía. Para lograr esto se necesita de novedosas técnicas de implementación de los algoritmos en conjunto con un estricto flujo de desarrollo que permite obtener resultados de excelencia en un corto plazo. La temática del tutorial se enfoca en describir en detalle el flujo de diseño de un transceptor óptico de alta velocidad que permita cumplir con las exigencias del mercado. Además, se exponen arquitecturas de alta complejidad de algoritmos típicamente utilizados haciendo énfasis en las técnicas de implementación.

Ing. Salvador E. Tropea (INTI)

Por primera vez en los más de 30 años desde la creación de las FPGAs es posible realizar diseños basados en FPGA utilizando únicamente software libre. En esta charla veremos cómo es posible realizar las diferentes etapas de diseño utilizando herramientas de Software Libre. Se expondrán ejemplos de placas de hardware libre y se presentarán herramientas de simulación y síntesis de Software Libre.

Ing. Salvador E. Tropea (INTI)

Dentro de la enorme flexibilidad de las FPGAs se encuentra la posibilidad de incluir una CPU en nuestro diseño, dejando así parte del problema a ser resuelto por software. Para estos fines existen dos grandes alternativas, utilizar FPGAs que incluyen una CPU (hardcores) o bien utilizar parte de los recursos reconfigurables de la FPGA para implementar una CPU (softcores). En esta charla se presentarán diferentes opciones para implementar sistemas con softcores, así como una breve comparación con las opciones basadas en hardcores. Como ejemplo de aplicación en esta edición se presentará la implementación de un Arduino basado en un softcore de AVR (Lattuino).

Lic. Miguel García (FCEN-UBA)

En este tutorial vamos a construir un sistema de co-diseño hardware/software para procesamiento de video en tiempo real. Partiendo de una solución que realiza el 100% del procesamiento en software vamos a optimizarla utilizando síntesis de alto nivel, para construir un IP Core de filtrado de imágenes. Los principales ejes del tutorial serán: Interfaz entre CPU+RAM e IP Core de filtrado utilizando AXI Stream y DMA. Técnicas de diseño en HLS y aplicación de directivas para mejorar el rendimiento. I/O de video utilizando la placa de desarrollo Zybo. Comparativa de rendimiento entre implementación 100% software y solución con co-diseño hardware/software.

Ing. Juan Cesaretti (Allegro)

El objetivo de la charla es cubrir los distintos aspectos relacionados al diseño, fabricación y evaluacion de los circuitos integrados en la actualidad. Se conversará sobre las responsabilidades e interrelaciones de los distintos miembros de un proyecto durante el diseño, los pasos involucrados en la fabricación de un IC y finalmente la evaluación del producto.

Ing. Rodrigo Melo (INTI), Bruno Valinoti (INTI)

La simulación de lenguajes HDL es un aspecto fundamental en el desarrollo de ASCIs digitales y lógica programable como FPGAs y CPLDs. Existen herramientas privativas consolidadas como Modelsim, que todos los fabricantes de FPGAs ofrecen en alguna variante, pero que son dependientes de hardware del dispositivo y poseen limitaciones en las licencias gratuitas que ofrecen. En este tutorial presentamos el uso de herramientas libres como GHDL (simulador de VHDL), iVerilog (simulador de Verilog) y GtkWave (visor de formas de onda), brindando información y ejemplos de modos de uso, así como también consejos y recomendaciones tendientes al desarrollo de IP cores portables.

Mg. Bioing. Eduardo Filomena, Mg. Bioing. Juan Manuel Reta (UNER)

Esta charla, tiene por objetivo plantear las particularidades e inconvenientes que se presentan al momento de implementar un sistema de amplificación, digitalización y procesamiento de señales electrofisiológicas como el Electrocardiograma, el Electroencefalograma, el Electromiograma, etc. aportando distintas soluciones tradicionales y modernas para cada uno de los casos. Se plantean conceptos como: modelo de interferencia a ruido de red, DRL o driver de pierna derecha, amplificación en continua versus amplificación en alterna y sustracción digital.

Proyecto Abierto BioAmp: Amplificador de Biopotenciales para adquisición y procesamiento de señales biomédicas.

Esp. Bioing. Jerónimo La Bruna (Laboratorio CES)

Los productos médicos deben cumplir con una serie de regulaciones y normas antes de poder comercializarse. El cumplimiento de estas regulaciones y normas debe tenerse en cuenta desde la conceptualización del producto médico para poder llegar al mercado rápidamente con un producto que haya probado ante un tercero que es, dentro de lo posible, seguro y eficaz. En este encuentro se explicarán los lineamientos básicos para llevar adelante el desarrollo de productos médicos en un campo altamente regulado.

Bioing. Juan Ignacio Cerrudo, Bioing. Albano Peñalva (UNER)

Se trata de un acercamiento a las principales tecnologías de Impresión 3D disponibles y en desarrollo actual. Aplicaciones: Se realiza una revisión sobre el proceso de generación de modelos 3D a partir de imágenes médicas y sus aplicaciones clínicas actuales como así también las tendencias en el avance tecnológico del sector. Se presentan las principales características y normas aplicables a los materiales empleados para impresión 3D en traumatología y odontología entre otros. Finalmente se presentan las principales experiencias realizadas por el Laboratorio de Prototipado Electrónico y 3D de la FIUNER en generación de modelos para planificación de cirugías, educación, prototipado mecánico y funcional entre otras.

Ramiro Verrastro, Emiliano Statello (UTN-FRBA)

Desarrollo de un método para realizar odometría visual en tiempo real, utilizando imágenes estereoscópicas combinadas con información obtenida por GPS, realizando localización en un mapa geo-referenciado. Utilizacion de un filtro de Kalman para fusionar la posición obtenida por el sistema de Visión con la obtenida mediante GPS de forma tal que cada medición es ponderada de acuerdo a su varianza. La combinación de ambas mediciones mediante el filtro de Kalman provee una trayectoria con menor error que las mediciones tomadas independientemente y completa tramos del recorrido en los cuales la información de los sensores es insuficiente, lo cual da muestra de la robustez del método. En este tutorial se muestran los aspectos principales de los algoritmos, su implementación práctica, el hardware utilizado y los detalles del prototipo con el cual se obtuvieron los resultados experimentales.

Ing. Claudio Verrastro (CNEA, UTN-FRBA), Juan Carlos Gómez (INTI, UTN-FRBA)

En el área del control de robots, los sistemas de aprendizaje son cada vez más utilizados para encontrar estrategias de comportamiento que sean óptimas en algún sentido. En particular el aprendizaje por refuerzos o recompensas. En este tutorial se presentan algoritmos muy populares como SARSAλ y QLearning. Se realiza una introducción teórica del tema y se muestran ejemplos y sus resultados. Se describen ventajas y desventajas de cada algoritmo y se obtienen conclusiones.

Ing. Eduardo Granzella (UTN-FRBA), Ing. Hernán Giannetta (INTI, UTN-FRBA ), Ing. Lucas Barrera (UTN, CONAE).

Se presentará la implementación en FPGA de Manipuladores robóticos utilizando compiladores GNU de programas, en la que se dará una introducción a la cinemática y dinámica de los manipuladores robóticos y a la implementación en FPGA del control del robot, así como la introducción y desarrollo de compiladores GNU para robots de N grados de libertad re-configurables. Además se presentará un robot móvil de dos ruedas, junto con el análisis de factores de divergencia de trayectoria utilizando un controlador DuinoBot, para lo que se hará una introducción al modelo de cinemática y dinámico utilizado, así como al controlador DuinoBot y se discutirá la influencia de los factores constitutivos, fricciones e interpoladores en la trayectoria del móvil.

Carlos Pantelides (ACSE)

Un recorrido por los conceptos fundamentales involucrados en la defensa de sistemas informáticos. Principios de seguridad de la información, autenticación y diseño. Orientado a estimular el modelo mental de seguridad. Conceptos teóricos, prácticos y experiencias reales.

Carlos Pantelides (ACSE)

Ejemplo integral de diseño, ataque y defensas de un sistema de autenticación. Ataques a la criptografía, ingeniería social. Defensa personal informática.

Carlos Pantelides (ACSE)

Escenarios de ataque, demo de buffer overflow sobre una aplicación vulnerable en EDU-CIAA-NXP. Ataques a ATMs.

Carlos Pantelides (ACSE)

Técnicas de testing de seguridad, Misuse cases. Ejemplo práctico con sensores.

Concurso de proyectos estudiantiles

IMPORTANTE: Cada proyecto participante, deberá instalar en el espacio asignado un póster tamaño A1 (597 x 841mm) con una descripción del proyecto, fotos, diagramas,etc.

Debajo del título debe indicarse la categoría en la cual participa.

FINALISTAS DEL CONCURSO:

Los titulares deberán confirmar su participación en el concurso hasta el 31 de julio proximo. Si asi no lo hicieran, su proyecto será dado de baja e ingresará en su lugar el proyecto suplente.

CATEGORIA A

Titulares

| A02 | Evaluación y detección de potenciales evocados sobre una interfaz cerebro computadora | |

| A03 | EsCoBa (Estructura de Control de Basura) | |

| A08 | Trazador de curvas de Semiconductores | |

| A09 | Dispositivo electrónico para medición no invasiva de glucosa en sangre | |

| A10 | SISTEMA BIOMÉDICO NO INVASIVO PARA EVALUACIÓN FISIOLÓGICA Y PREDIAGNÓSTICO DE CONDICIONES DE ANEMIA, HIPOXEMIA E HIPERTENSIÓN |

Suplente

| A07 | Plataforma basada en FPGA para prototipado de SDR |

CATEGORIA B

Titulares

| B09 | Diseño y desarrollo de un drone con sistema de control de velocidad y estabilidad implementado con FPGA. | |

| B15 | Enlace IR-BFSK basado en FPGA, para uso didáctico | |

| B17 | M-Codex: Vocoder Digital Implementado en ARM Cortex M4 | |

| B22 | Sintetizador Digital de Audio con Filtro, Efectos y Comunicación por USB bajo LPCXpresso y FreeRTOS | |

| B23 | Robot Seguidor de línea de bajo costo y diseño abierto |

Suplente

| B01 | Smart Coffee |

CATEGORIA C

| C01 | Consola DMX | |

| C02 | WATERSPILL | |

| C03 | DrumZZ – bateria MIDI | |

| C04 | Sistema de Control de Timbres | |

| C05 | Desarrollo de un controlador de semáforos portátiles |

CATEGORIA CIAA

Titulares

| CIAA01 | Sistema de reconocimiento de palabras para la EDU-CIAA | |

| CIAA02 | Port del Firmware CIAA para plataformas basadas en FPGA con softcore LEON 3 | |

| CIAA04 | Monitor de Tracción con CIAA | |

| CIAA05 | Visualización 3D del comportamiento de un objeto | |

| CIAA07 | Sistema de cultivo hidropónico basado en la EDU-CIAA |

Suplente

| CIAA06 | Control de temperatura para soldadura SMD, utilizando la EDU-CIAA |

El Simposio Argentino de Sistemas Embebidos (SASE) busca incentivar entre los estudiantes universitarios y los jóvenes profesionales el interés por los sistemas embebidos. En ese contexto desde la primera edición del SASE, se lanzó el “Concurso de Proyectos Estudiantiles” (CPE) con el aporte de las empresas auspiciantes del evento.

Categorías del Concurso

El concurso se desarrollará en cuatro categorías.

Categoría A: Proyectos desarrollados como trabajo final de grado universitario o como Trabajo Final de una Carrera de Especialización.

Categoría B: Proyectos desarrollados como trabajo asociado a una cátedra universitaria o bien en el ámbito de una carrera terciaria.

Categoría C: Proyectos desarrollados por alumnos de Escuelas Técnicas Secundarias.

Categoría CIAA: Proyectos realizados utilizando la CIAA-NXP, EDU-CIAA-NXP, picoCIAA o que contribuyan al proyecto CIAA en cualquiera de sus versiones. Puede inscribirse cualquier persona sin importar su nivel formal de estudios.

Premios para las distintas categorías

| Categoría | 1er premio | 2do premio |

| A | $ 8.000 | 1 EDU-CIAA |

| B | $ 6.000 | 1 EDU-CIAA |

| C | $ 4.000 | 1 EDU-CIAA |

| CIAA | $ 6.000 | $ 4.000 |

Además se entregarán Diplomas a:

- Los estudiantes premiados

- Los Docentes Tutores de los mismos

- La/s Institución/es a las que pertenezcan

Jurados del CPE SASE 2017:

- Ing. Gerardo Sager (UNLP). Coordinador del Jurado

- Ing. Marcelo Romeo (UTN-FRBA, UNSAM, UP)

- Esp. Lic. Juan Agustin Bassi (FIUBA)

- Esp. Ing Patricio Bos (FIUBA)

- Esp. Ing. Facundo Larosa (UTN-FRH, FIUBA)

- Esp. Ing. Julián Iglesias (FIUBA, Tenaris)

- Ing. Ezequiel Espósito (FIUBA, DebMedia)

Becas de alojamiento

A partir del auspicio de universidades, empresas e instituciones el SASE2017 organiza un programa de becas de alojamiento para estudiantes y docentes universitarios de la República Argentina y países de la región. El programa de becas del SASE ha sido una herramienta muy eficaz durante los últimos 6 años para federalizar el evento y contribuir a generar un espacio de encuentro sostenido por el esfuerzo de docentes y alumnos que año tras año han colaborado en la organización de los contingentes. A partir de los fondos disponibles este año se ofrecerán 551 becas parciales de alojamiento. La idea es que cada Unidad Académica aporte un porcentaje de los fondos necesarios, a través del cobro a cada asistente o de su propio presupuesto. El alojamiento de aquellos que participen a través de un contingente tendrá un costo de $200 por persona las tres noches: martes 8, miércoles 9 y jueves 10 de agosto.

Por favor cumplir con la lista de asistentes entregada, sin cambios ni bajas de último momento.

Condiciones de Alojamiento:

- El servicio es contratado para las fechas que van del 8 o 9 al 11 de agosto de 2017 inclusive (por 2 o 3 noches) dependiendo de lo que cada coordinador informó en la planilla del contingente.

El horario de check in es a partir de la 1pm y el de check out a las 10 am.

No Incluye toalla pero algunos Hostels podrán ofrecer el uso de las mismas por $30. adicionales, sujetos a disponibilidad de stock.

El hostel no cobrará depósito de llaves.

El hostel deberá contar con recepción nocturna SIN excepción.

Los dormitorios serán de hasta 8 camas.

En caso de poner a disposición habitaciones dobles, estas deberán ser con camas separadas.

Los baños en todos los casos serán compartidos, en el caso de las privadas podrán ser privados o compartidos dependiendo del hostel.

En el caso de que los estudiantes deseen extender su estadía por fuera de las fechas estipuladas entre ACSE y la CAH la responsabilidad del pago y reserva correrá por su cuenta y del Hostel (que podrá aceptar o no, dependiendo de su disponibilidad) y bajo ningún punto de vista la CAH se hará responsable de cobrar esas noches extra.

Al momento del arribo del grupo de pasajeros, si hubiera algún problema con la asignación de plazas estipuladas y/o condiciones pactadas en este convenio, ANTES de tomar cualquier decisión, un responsable del grupo o de ACSE se comunicará con la coordinadora de la CAH para ver cómo se resuelve.

# | UNIVERSIDAD | PROVINCIA | DOCENTE RESPONSABLE | LISTADO ASISTENTES | HOSTEL ASIGNADO | DIRECCIÓN | ||

1 | UTN-FRN | Neuquén | Gustavo Monte | 15 | www.hostelsol.com.ar | LIMA 1169 | ||

2 | UNT -FaCEyT | Tucumán | Martín Juarez | 52 | http://milhousehostel.com/ | Hipólito Yrigoyen 959 | ||

3 | UTN-FRBB | Bs. As. | Christian Galasso | 7 | www.hostelsuites.com | Florida 328 | ||

4 | UNER | Entre Ríos | Gonzalo Cuenca | 53 | 29 http://milhousehostel.com/ | 24 http://www.rockhostel.com.ar | Av. de Mayo 1245 | Av. Rivadavia 1587 |

5 | UNSL | San Luis | María Julia Xacur | 38 | 20 www.playhostel.com | 18 www.artfactorypalermo.com.ar | Guatemala 4636 – Palermo | COSTA RICA 4353 |

6 | UTN-FRT | Tucumán | Jorge Buabud | 54 | www.hostelpampa.com.ar | GUATEMALA 4778 | ||

7 | DCIC-UNS | Buenos Aires | José Moyano | 6 | http://viluzyentrehostel.com.ar | México 2233 | ||

8 | UTN FRR | Chaco | Rodrigo Vigil | 2 | www.hostelsuites.com | Florida 328 | ||

9 | UTN-FRC | Córdoba | Elías Cáceres | 57 | 25 http://www.bastop.com/ | 32 https://www.hostelestoril3.com | Rivadavia 1194 | Av. de Mayo 1385 |

10 | IUA | Córdoba | Jose María Ducloux | 9 | http://puertolimonhostel.com/ | Chacabuco 1080 | ||

11 | UNS-DIEC | Bs. As. | Gustavo Ramoscelli | 11 | http://puertolimonhostel.com/ | Chacabuco 1080 | ||

12 | FI-URU | Uruguay | Leonardo Steinfeld | 18 | http://milhousehostel.com/ | Av. de Mayo 1245 | ||

13 | UTN-FRSN | Bs. As. | Sergio Ponce | 18 | www.hostelclub.com | Viamonte 857 | ||

14 | UTN-FRLR | La Rioja | Ricardo Maldonado | 26 | www.ostinatto.com | Chile 680 | ||

15 | UNMdP | Bs. As. | Maximiliano Antonelli | 18 | www.hostelsol.com.ar | LIMA 1169 | ||

16 | UNPSJB | Chubut | Martín Colombo | 3 | www.hostelsol.com.ar | LIMA 1169 | ||

17 | UTN-FRM | Mendoza | Adrián Sierra | 2 | www.hostelclub.com | Viamonte 857 | ||

18 | UNSJ | San Juan | Eugenio Orozco | 10 | www.hostelsuites.com | Charcas 4752 | ||

19 | UNLPm | La Pampa | M. A. Martín | 6 | www.artfactorypalermo.com.ar | COSTA RICA 4353 | ||

20 | UNR | Santa Fe | Ignacio Sosa | 46 | 25 www.06centralhostel.com | 21 www.hostelsuites.com | Maipu 306 | Florida 328 |

21 | UNNE FCENyA | Corrientes | Jeremías García | 40 | 20 http://artfactoryba.com.ar/es/hostel/ | 20 http://www.americahostel.com.ar/ | Piedras 545 | Chacabuco 718 |

22 | UNCA | Catamarca | Walter Herrera | 18 | www.hostelsuites.com | Charcas 4752 | ||

23 | UNC | Córdoba | Agustín Martina | 30 | 20 http://www.sabaticohostel.com.ar/ 10 http://viluzyentrehostel.com.ar | Mexico 1410 Mexico 2233 | ||

24 | UNNOBA | Bs. As. | Adrián Jaszczyszyn | 3 | www.hostelsuites.com | Charcas 4752 | ||

25 | UNRC | Córdoba | Damián Primo | 5 | www.06centralhostel.com | Maipu 306 | ||

26 | UTN-FRP | Entre Ríos | Andrés Mendez | 4 | https://www.hostelestoril3.com’ | Av. de Mayo 1385 | ||

Organizadores Locales

Coordinación general

Ariel Lutenberg, FIUBA

Programa 2017