SASE 2011

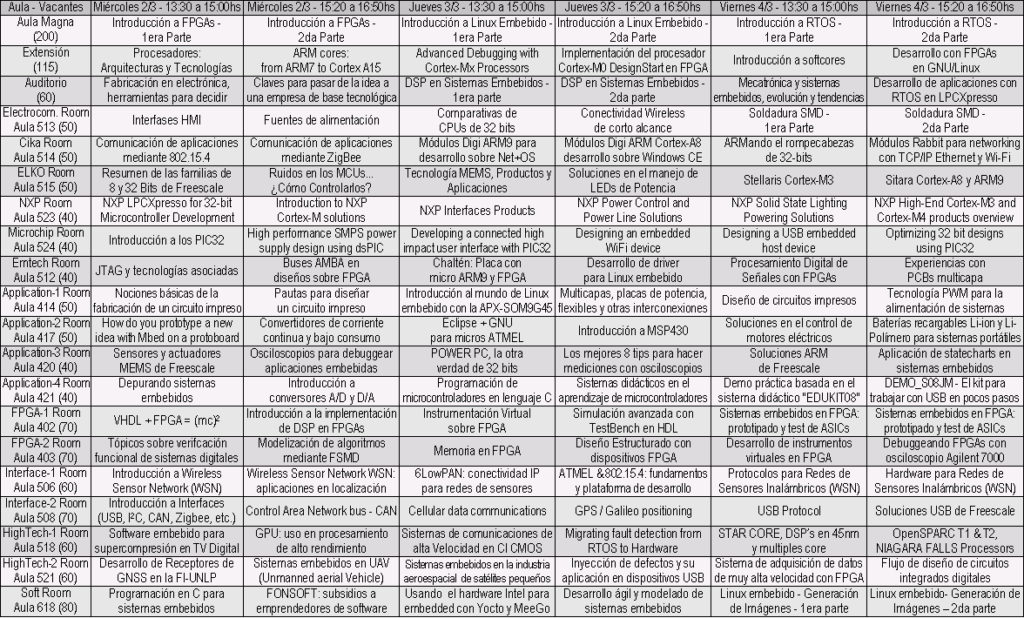

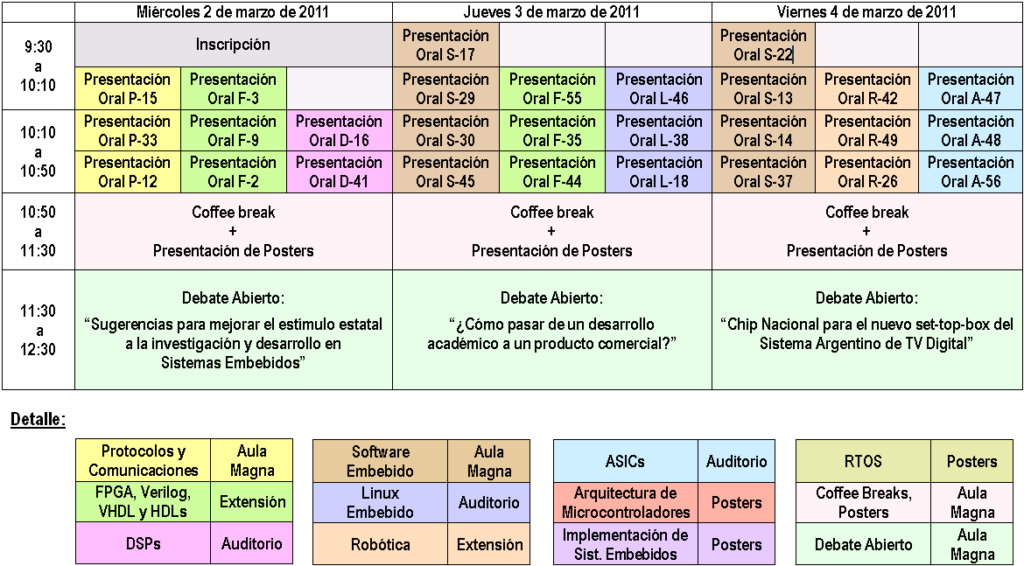

El Simposio Argentino de Sistemas Embebidos, SASE2011, se realizó en la Universidad Tecnológica Nacional – Facultad Regional Buenos Aires (UTN-FRBA), Buenos Aires, Argentina, del miércoles 2 al viernes 4 de marzo de 2011. En el mismo se realizaron las siguientes actividades:

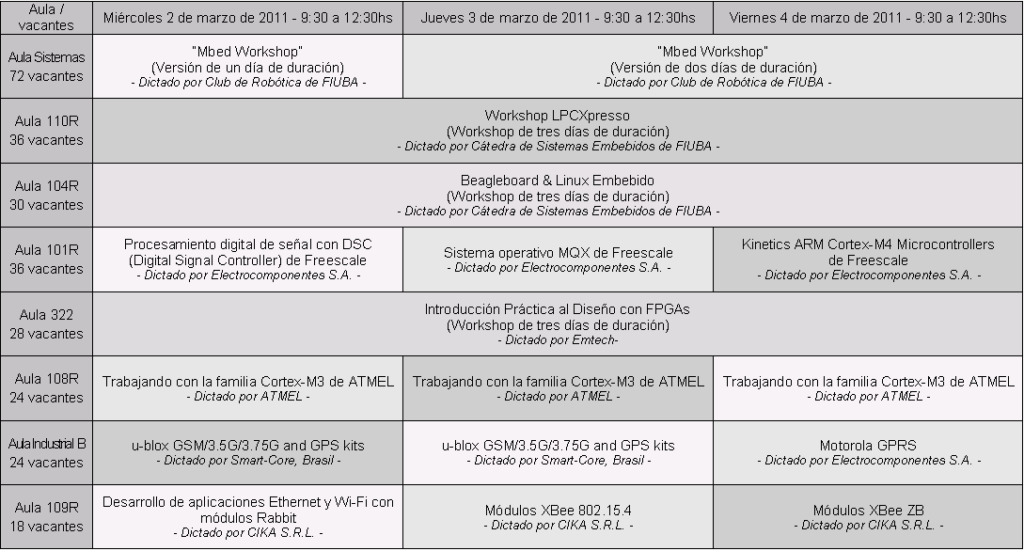

Talleres en la modalidad hands-on.

Dictado por: Sergio R. Caprile, Cika Electrónica S.R.L.

Configuración y utilización. En el workshop se realizarán pequeñas redes entre los participantes.

Requisitos: Se requiere conocimientos de programación en C; Se requiere tener conocimientos básicos de comunicaciones serie; Se sugiere asistencia al tutorial “Comunicación de aplicaciones mediante ZigBee. Presentación de módulos XBee ZB”

Dictado por: Sergio R. Caprile, Cika Electrónica S.R.L.

Su configuración y utilización.

Vacantes disponibles: 18 personas (9 PCs)

Requisitos: Se requiere conocimientos de programación en C; Se requiere tener conocimientos básicos de comunicaciones serie; Se sugiere asistencia al tutorial “Comunicación de aplicaciones mediante 802.15.4. Presentación de módulos XBee 802.15.4”

Dictado por: Sergio R. Caprile, Cika Electrónica S.R.L.

Desarrollo de aplicaciones con conectividad Ethernet y Wi-Fi con módulos Rabbit. En el workshop se guía a los participantes en el desarrollo de pequeñas aplicaciones con conectividad TCP/IP.

Vacantes disponibles: 18 personas (9 PCs)

Requisitos: Se requiere conocimientos de programación en C; Se requiere tener conocimientos básicos de networking.

Dictado por: Ignacio Zaradnik, de Electrocomponentes S.A.

El presente workshop nos introducirá a esta tecnología, a los servicios que soporta la red y sus aplicaciones. Veremos los productos que Motorola nos ofrece y realizaremos ejemplos de comunicaciones de datos a través de CSD, enviaremos y recibiremos mensajes de texto, transmitiremos datos y enviaremos mails a través del GPRS/EDGE, y finalmente hablaremos de las consideraciones de hardware para desarrollar un producto.

Requisitos: No requiere experiencia previa.

Vacantes disponibles: 28 personas (14 PCs)

Dictado por: Ricardo Adulis y Ricardo Nunes, SmartCore , Brasil.

On the hands-on we will demonstrate the usage of GSM/3.5G/3.75G and GPS kits as follows:

- Network register;

- Open GPRS communication;

- Create, read and write socket;

- Get GPS position thru USB and UART;

- Test cold start time with and without AssistNow (AGPS);

- Get GPS position thru GSM UART via AT commands.

Vacantes disponibles: 28 personas (14 PCs)

Requisitos: Conocimientos previos de comunicaciones serie y TCP/IP

Dictado por: Santiago Morrison <Santiago.Morrison@atmel.com>, ATMEL.

Se trabajará con módulos basados en el micro ATSAM3S, cuyo core es un Cortex M4, y también se hará hincapié en las herramientas de desarrollo gratuitas. Para ello , se empleara como ambiente de desarrollo Eclipse como compilador GCC. En los diferentes ejercicios se podrán ver conceptos de distintos periféricos y cómo bajar la aplicación a través de su bootloader.

Vacantes disponibles: 24 personas (12 PCs)

Requisitos: conocimientos de Lenguaje C, noción de arquitectura de microcontroladores.

A cargo de: Guillermo Guichal, Emtech / UTN-FRBB y Sebastián García FI-UBA / Slabs

En este taller «manos a la obra» de tres mañanas (9hs reloj), se desarrollará un proyecto concreto sobre una plataforma de hardware nacional basada en dispositivos Microsemi (Actel) de lógica programable (FPGA). De manera intensiva y durante el proceso de desarrollo del proyecto propuesto, se irán brindando los conceptos básicos, a medida que se vayan presentando los obstáculos. El principal objetivo de aprendizaje es lograr, mediante un enfoque altamente práctico, atravesar con éxito las etapas de desarrollo, trabajando con un flujo de diseño típico basado en el lenguaje VHDL, realizando simulaciones y finalizando con la aplicación funcionando sobre la placa.

Vacantes disponibles: 28 personas (12 PCs)

Requisitos: Estudiantes de electrónica o ingenieros con conocimientos básicos de técnicas digitales (lógica combinacional (compuertas) y secuencial (flip-flops), memorias, etc.) y desarrollo de aplicaciones basadas en microcontroladores.

A cargo de: Freescale y Dpto. de Ingeniería de Electrocomponentes S.A., Buenos Aires, Argentina.

“Kinetis ARM Cortex-M4 Microcontrollers” 32-bit Kinetis MCUs represent the most scalable portfolio of ARM® Cortex™-M4 MCUs in the industry. The first phase of the portfolio consists of five MCU families with over 200 pin-, peripheral- and software compatible devices with outstanding performance, memory and feature scalability. Enabled by innovative 90nm Thin Film Storage (TFS) flash technology with unique FlexMemory (configurable embedded EEPROM), Kinetis features the latest low-power innovations and high performance, high precision mixed-signal capability. Kinetis MCUs are supported by a market-leading enablement bundle from Freescale and ARM 3rd party ecosystem partners.

Vacantes disponibles: 36 personas (12 PCs)

Requisitos: experiencia previa en la programación de microcontroladores en lenguaje C.

A cargo de: Dpto. de Ingeniería de Electrocomponentes S.A.

¿Qué es un sistema operativo de tiempo real y cuáles son sus utilidades? Descripción del sistema MQX, sus características y ventajas. Descripción y Hands-on de los elementos que forma un sistema operativo. Stack para soluciones Ethernet y USB.

Vacantes disponibles: 36 personas (12 PCs)

Requisitos: Experiencia previa en la programación de microcontroladores en lenguaje C.

A cargo de: Ing. Gustavo Parlanti, de la Universidad Nacional de Córdoba, junto al Departamento de Ingeniería de Electrocomponentes, Cordoba, Argentina.

Hands-On Workshop de Procesamiento Digital de Señales utilizando DSC de Freescale. La idea del workshop es aprender el mecanismo de trabajo para el desarrollo de una aplicacion de DSP en el entorno de trabajo Codewarrior de Freescale realizando adquisicion, filtrado y analisis espectral de una señal usando DSC de la familia 56f8xx de Freescale.

Vacantes disponibles: 36 personas (12 PCs)

Requisitos: Experiencia previa en la programación de microcontroladores en lenguaje C.

Tutoriales

Charlas técnicas de 90 minutos de duración, agrupadas por temas.

Disertante: Víctor Grimblatt, Synopsis, Santiago de Chile, Chile.

Diseñar un circuito integrado digital es desarrollar un conjunto de tareas que permiten transformar una idea en un circuito que funciona y que cumple con la funcionalidad deseada. A este conjunto de tareas se le llama flujo de diseño, el que será revisado en detalle durante el tutorial. Cada etapa del flujo será revisada en detalle explicando su objetivo, sus entradas y salidas y las herramientas que permiten desarrollarla con éxito.

Ing. Santiago Morrison, Atmel, Buenos Aires, Argentina.

9) Imagen del Usr

10) BuildRoot -Que es. -Modificando Buildroot. –Versiones. -Target Architecture –Drivers -Selección de paquetes. –BusyBox. -Añadiendo paquetes. -Finalmente podemos compilar….., como? –Imágenes

11) Drivers –Conceptos -Espacio User -Espacio Kernel -Tipos de Drivers Char, Block,USB ,etc -Compilando y corriendo modulos -Char Drivers -Concepto, Estructuras, métodos -Técnicas de Debugger Comandos avanzados de Drivers -Time, Delays and Deferred Networks – Comunicándose con Hardware. -Interrupt Handling -Links de interés

12) Aplicación -Algunos ejemplos -Entradas Salidas-Timers-PWM.

Disertante: Ing. Juan Martín Semegone, CoNAE-IAR., Buenos Aires, Argentina.

Sun Microsystems hace relativamente poco tiempo abrió los diseños de los procesadores UltraSPARC T1 y UltraSPARC T2. Las versiones con código abierto son llamadas OpenSPARC T1 y OpenSPARC T2. Sun promovió el auge a nivel académico y en general del código abierto de estos procesadores, junto con la versión libre del OS Solaris, el OpenSolaris. Estos procesadores permiten ahora ser implementados en FPGA y es posible realizar sistemas embebidos con la arquitectura más grande que existe de código abierto. Así, es posible desarrollar un chip con 8 procesadores en paralelo cuya arquitectura es de 64 bits. Ya existe un port preliminar del RTOS RTEMS para Open SPARC T1.

Disertante: Freescale y Dpto. de Ingeniería de Electrocomponentes S.A., Buenos Aires, Argentina.

Características del estándar; Tipos de transferencias; Clases; Proceso de comunicación; Productos y Herramientas Freescale; Stacks de software. Descargar el tutorial completo.

Disertante: Ing. Pablo Godoy, ITIC, UNCuyo, Mendoza, Argentina.

Situación Actual, Alternativas y Futuro. Definición y campos de aplicación. Hardware que compone una WSN. Componentes del nodo. Protocolos de comunicación. Nuestro trabajo en el ITIC (IDIT): i. Influencia de obstáculos comunes en aplicaciones en agronomía y sensado de variables ambientales sobre la confiabilidad del enlace. ii. Efecto sobre la confiabilidad del enlace de condiciones atmosféricas adversas, como ser lluvia. iii. Efecto sobre la confiabilidad del enlace de la posición de los nodos.

Disertante: Agilent y Dpto. de Ingeniería de Electrocomponentes S.A., Buenos Aires, Argentina.

Introducción. Usando un MSO para la validación de las funcionalidades de una FPGA. Parámetros a medir en aplicaciones con FPGA; Consejos para una buena medición; Ejemplos; Productos de la serie 7000.

Dr. Alfonso Chacón Rodriguez, ITCR, Costa Rica.

Continuación de la 1era parte.

Disertante: Ing. Roberto Simone, EDUDEVICES, Buenos Aires, Argentina.

Demostración práctica basada en la placa «DEMO_S08JM» donde se abordarán los mundos del MCU MC9S08JM60 de la familia de microcontroladores HC9S08 de Freescale Semiconductor y de la PC bajo sistema operativo Windows de Microsoft en una aplicación USB (Universal Serial Bus) típica. El curso tiene por objetivo demostrar la facilidad de implementación de aplicaciones que utilizan esta popular interface de comunicaciones contando con las herramientas de hardware y software necesarias para ello. Los temas más importantes del curso son los siguientes: Principios Básicos de la interface USB, Que es la interface USB?, Características de Hardware y Software, Tipos de USB disponibles, Conceptos de: Endpoint – pipe – Bulk – Sincrónico, PID / VID, etc., Aspectos desde el lado del MCU (Librería USB – Firmware – Hardware), Librerías USB – Stack USB para el MCU JM60, Descripción del Firmware de base para utilizar en USB, Hardware básico de un sistema USB, Aspectos desde el lado de la PC (Drivers, Archivos «.inf», etc.),Creación y uso de los archivos de información USB «.INF», Drivers necesarios para que windows reconozca al dispositivo USB, Otros aspectos a tener en cuenta. Aplicación práctica basada en Visual C Sharp empleando la placa DEMO_S08JM con MC9S08JM60.

Disertante: Ing. Juan Manuel Cruz, FIUBA / UTN-FRBA, Buenos Aires, Argentina. Introducción, estado del arte, problemática general, criterios de diseño, casos típicos de estudio y ejemplos de aplicación. Descargar el tutorial completo

Disertante: Ing. Ricardo Teijeiro, Probattery, Buenos Aires, Argentina.

La continua miniaturización de los sistemas electrónicos, hace que la batería tenga un rol cada vez más importante en dos aspectos fundamentales: portabilidad y autonomía. En la actualidad, las baterías de Li-ion y Li-Polímero son las elegidas por los diseñadores de equipos electrónicos de alta tecnología. Se explicará su funcionamiento y cómo incorporar estas nuevas baterías en los desarrollos electrónicos.

Concurso de proyectos estudiantiles

El Jurado del Concurso de Proyectos Estudiantiles, compuesto por:

- Ing. Roberto Barneda (UTN-FRBA)

- Ing. Daniel Di Lella (ELKO/Arrow S.A.)

- Ing. Gustavo Mercado (UTN-FRM)

- Ing. Gerardo Sager (UNLP)

ha determinado que los siguientes proyectos estudiantiles son los ganadores del Concurso dado el uso innovador y creativo de las tecnologías disponibles, el realismo en la solución propuesta, la adecuación a normas internacionales de calidad y/o performance, la capacidad de comunicación de la problemática abordada y la clara comparación de la solución propuesta con otras disponibles mundialmente.

Los Proyectos Estudiantiles y los Emprendimientos Tecnológicos seleccionados para la etapa final de los concursos del SASE 2011 serán expuestos durante los coffee breaks en el aula 105 de la UTN-FRBA, y los ganadores serán anunciados el viernes 4 de Marzo a las 18:40hs en el aula magna de la UTN-FRBA.

Ganadores de los Concursos del SASE2011

Categoría A – Trabajos finales de graduación universitaria o terciaria

Primer Premio: Lapix

Universidad de la República (Uruguay)

Autores: Mauro Andrés Di Lonardi, Pablo Martín Iguini, Diego Vigano

Proyecto de Fin de Carrera

Tutor: Juan Pechiar

En este proyecto se construye un prototipo funcional de un lápiz electrónico inalámbrico que permite escribir y dibujar sobre las pantallas de las XO (computadoras del Plan Ceibal), o cualquier superficie lisa, y que además funciona como un sustituto del mouse. Puede utilizarse en cualquier PC con sistema operativo Linux y es portable a Windows.

Cuenta con un lápiz electrónico inalámbrico, un dispositivo de recepción, un driver y un acrílico protector. El lápiz electrónico emite señales desde la punta. Dispone de 2 botones, uno primario, otro secundario y tiene un interruptor de encendido. El receptor se encarga de detectar las señales emitidas por el lápiz, procesarlas y comunicarse con la PC anfitriona a través del puerto USB. Para esto se utiliza un PIC32. El Driver es el software instalado en la PC que se encarga de recibir la información enviada por el receptor, procesarla y realizar el despliegue correspondiente en pantalla. Se cuenta con un área de cobertura equivalente a una hoja de tamaño A4 con una resolución de 136DPI en un 90% del área.

Segundo Premio: Sistema de control de un microdisplay LCD

Universidad de Buenos Aires

Autor: Ariel Burman

Tesis de Ingeniería Electrónica

Tutores: Dr. Ariel Lutenberg, Dr. Fernando Perez Quintián.

Los moduladores espaciales de luz son sistemas ópticos que permiten modificar en tiempo real, la amplitud y la fase de la luz que los atraviesa. Habitualmente, el elemento central de estos sistemas es un microdisplay. Los microdisplays son displays de cristal líquido donde el tamaño de los píxeles es del orden de 10 a 40um. Generalmente, el alto costo de los SLMs, del orden de decenas de miles de dólares, resulta prohibitivo para los laboratorios de óptica. Frecuentemente se suelen armar SLMs precarios a partir del desguace de proyectores de video. Esto presenta dos inconvenientes: por un lado, la dificultad de disponer de varios SLMs de características similares. Por otro lado, la necesidad de utilizar una PC para generar las señales que emplea el SLM, debido a que los circuitos de control de los proyectores están diseñados para trabajar con señales de video. El equipo desarrollado consiste en un SLM utilizando un microdisplay de venta comercial, lo cual garantiza la repetibilidad del producto.

El esquema propuesto consiste principalmente en una CPLD que genera las señales de sincronismo del microdisplay, una memoria para almacenar distintas imágenes, un conversor DAC para cargar la imagen en el microdisplay y un microcontrolador que realiza el control general del sistema. De esta forma se logra utilizar el microdisplay sin la necesidad de trabajar con señales de video. El prototipo resulta significativamente más económico que los SLMs comerciales y, por ende, ofrece una alternativa en dispositivos para la investigación en óptica en el país. Las fotos presentan el prototipo desarrollado y una experiencia donde se observa una imagen generada desde el circuito controlador, utilizando la notebook de fondo, como luz de backlight.

Mención de Honor: Certificación de IP4JVM

Universidad de la República (Uruguay)

Autores: Daniel Enrique Rosano Lorenzo

Proyecto de Grado

Tutor: Ariel Sabiguero Yawelak

Durante varios años en la UdelaR se ha venido desarrollando una versión de IPv6 en Java y para Java, llamado IP4JVM, el cual es un producto con un grado importante de madurez, ya que se encuentra en su 4ta generacion. La implementacion se integra al OpenJDK 1.6 como una libreria mas y hace que éste se independice de los servicios de networking del sistema operativo. Al día de hoy se cuenta con implementaciones de los protocolos IPv6, ICMPv6, UDP, TCP, DHCPv6, entre otros. El objetivo del proyecto es complementar los protocolos ya existentes y certificar el producto (IP4JVM) de acuerdo al estandar definido por el IPv6 Ready Logo. Para ello es necesario que la implementación existente pase los tests de interoperabilidad y conformance del v6RL. La ejecucion de este proyecto de grado no solo es un paso importante para tener un producto de calidad que cumple con los estandares internacionales; sino ademas permite completar el proceso de calidad de la implementacion existente, verificando ademas la completitud y la correctitud de los protocolos implementados.

Al ser un proyecto de testing, el proyecto no posee una implementacion propia. Sin embargo los resultados que se desprenden de la corrida de los tests, resulta muy útil a la hora de realizar modificaciones al codigo original para hacerlo cumplir con los estandares de calidad definidos por la organizacion especializada en IPv6 (IPv6 Forum). La principal ventaja que proporciona el proyecto es la de trabajar en un ambiente virtualizado, mediante el uso de varias maquinas virtuales, con herramientas de testing semi-automáticas que permiten a un tester realizar el proceso de testing/corrección de errores con una única PC, en un tiempo mucho menor al que necesitaría para verificar los tests manualmente.

Categoría B – Proyectos de una materia universitaria o terciaria

Primer Premio: Audio Fingerprint

Universidad de la República (Uruguay)

Autores: Daniel Eduardo Aicardi, Edgardo Anselmo Vaz, Melina Rabinovich

Procesadores digitales de señal

Tutor: Juan Cardelino

¿A quién no le ha pasado escuchar una canción en la radio y querer saber cómo

se llama?. Que bueno sería tener un medio simple de usar, que nos permitiera de

manera rápida saber como se llama esa canción. Es útil además, con fines de

contralor, saber que canciones y cuantas veces fueron emitidas por una radio, a fin de

verificar los derechos de autor. Así mismo el sistema puede ser utilizado para

generación de estadísticas sobre la publicidad emitida por una emisora.

Una huella es una manera de caracterizar de forma única una señal de audio, mediante un resumen de su contenido. El objetivo general del proyecto es el reconocimiento de canciones a partir de su huella característica. A partir de una señal de audio a la entrada del DSP, se genera su huella de audio y se busca si la misma coincide con alguna de las huellas almacenadas en memoria. El método para la generación de la huella de audio es el cálculo de la frecuencia fundamental (f0) en el tiempo. Se toman intervalos de tiempo (enventanado) y se calcula f0 en cada uno de ellos. El conjunto de f0 halladas conforman la huella. Para la comparación de la huella de la señal de entrada contra las guardadas en la base de datos, se define un umbral con el fin de evitar falsos positivos y falsos negativos. Los resultados se visualizan en un display LCD16x2.

Segundo Premio: Implementación en Hardware Reconfigurable de un Microprocesador Didáctico: La Simplez

UTN-Facultad Regional Mendoza

Autores: Héctor Daniel Peralta, Martín Ariel Montero

Técnicas Digitales II

Tutor: Pablo A. Salvadeo

El proyecto consiste en la implementación de un microprocesador didáctico, Simplez, sobre un FPGA utilizando VHDL para la descripción. El fin de este proyecto es mejorar la experiencia educativa de los alumnos a través de la utilización de un microprocesador que se pueda construir, modificar y utilizar.

El proyecto consiste en la implementación de un microprocesador didáctico, Simplez, sobre un FPGA utilizando VHDL para la descripción. El desarrollo consiste en primera instancia en dos descripciones del microprocesador una utilizando el estilo estructural y otra el funcional. El propósito de esta primera parte es comparar los recursos tanto materiales como temporales de las implementaciones. La segunda etapa agrega un bloque llamado programador. Éste permite tomar un programa en ensamblador, traducirlo y volcarlo a la memoria para ser ejecutado por el microprocesador. La tercer etapa permite el manejo de dos periféricos: un teclado y un monitor, haciendo posible interactuar a través de éstos con el sistema. Cada una de las etapas agrega módulos en hardware que vuelven el sistema más versátil.

Mención de Honor: Procesador de Efectos

Universidad de Buenos Aires

Autores: Gonzalo Javier Brusco

Seminario de Electrónica: Sistemas Embebidos

Tutor: Pablo Gómez.

El presente proyecto se trata de un procesador de efectos de sonido portátil con una intuitiva interface a panel táctil. Por un lado se conecta en serie la música o sonido que se desea procesar, y luego mediante el panel táctil se decide que efectos aplicarles para su presentación en el otro extremo en tiempo real. Su sencillez de uso y perfil multitarea lo hacen un proyecto muy interesante el cual es manipulable simplemente con la presión del dedo en el panel. Este proyecto, el cual puede utilizarse conectado a amplificadores de guitarra o bajo, a sintetizadores y mezcladoras, puede enfocarse a músicos tanto profesionales en grabación de álbumes como a músicos novatos en busca de diversión.

La implementación del producto se basa en el muestreo del sonido ingresante en el microcontrolador y posterior procesamiento de acuerdo al efecto a considerar. El muestreo se realiza mediante el ADC utilizando dos buffers de entrada que se llenan en continuado con las muestras que permiten el procesamiento continuo de cada bloque. Luego se ubican las muestras procesadas en otros dos buffers de salida que se irán procesando también en continuado hacia el DAC. El transporte de las muestras a través del microcontrolador se realiza mediante DMA, lo cual nos permite mayor flexibilidad en el uso del micro y mayor performance. A su vez también se obtiene la posición del dedo en el panel táctil cada ciertos intervalos en busca de seleccionar los coeficientes del filtro correcto almacenado en memoria. Luego se procesa la información y el resultado es ubicado en los buffers de salida por DMA, repitiéndose el proceso.

Concurso de Emprendimientos Tecnológicos

El Simposio Argentino de Sistemas Embebidos (SASE) busca promover el desarrollo de la industria local en el área de los sistemas embebidos. En ese contexto se lanza el «Concurso de Emprendimientos Tecnológicos» con el aporte del Programa de Área Estratégica (PAE) Nº 37079 de Micro y Nano Electrónica de la Agencia Nacional de Promoción Científica y Tecnológica (Agencia) y el apoyo de los fondos de inversión InnovaTekne y Equitas Ventures.

La participación en el concurso es libre y gratuita y no existe ningún requisito en cuanto a la edad, filiación (pertenencia a una universidad o empresa) o formación académica de los participantes, excepto por la condición de que ninguno de los miembros del equipo postulante puede ser parte del jurado del concurso. Los equipos postulantes pueden estar conformados por cualquier cantidad de miembros.

En el concurso se valorará la viabilidad comercial y financiera de la propuesta, el uso innovador y creativo de las tecnologías disponibles, el realismo en la solución propuesta, la adecuación a normas internacionales de calidad y/o performance, la capacidad de comunicación de la problemática abordada, la clara comparación de la solución propuesta con otras disponibles mundialmente, etc. Para participar del concurso no es necesario mostrar un prototipo funcional del sistema, pero la presentación de un prototipo será valorizada por el jurado.

Los dos mejores proyectos de recibirán cada uno un premio de $3000.

El Jurado compuesto por:

- Cdr. Leopoldo Bibiloni (InnovaTekne)

- Ing. Manuel Greco (CADIEEL)

- Ing. Pablo Mandolesi (UNS)

ha determinado que los siguientes proyectos son los ganadores del concurso dada la viabilidad comercial y financiera de la propuesta, el uso innovador y creativo de las tecnologías disponibles, el realismo en la solución propuesta, la adecuación a normas internacionales de calidad y/o performance, la capacidad de comunicación de la problemática abordada y la clara comparación de la solución propuesta con otras disponibles mundialmente. Cada uno de estos proyectos recibirá un reconocimiento económico de $2000.

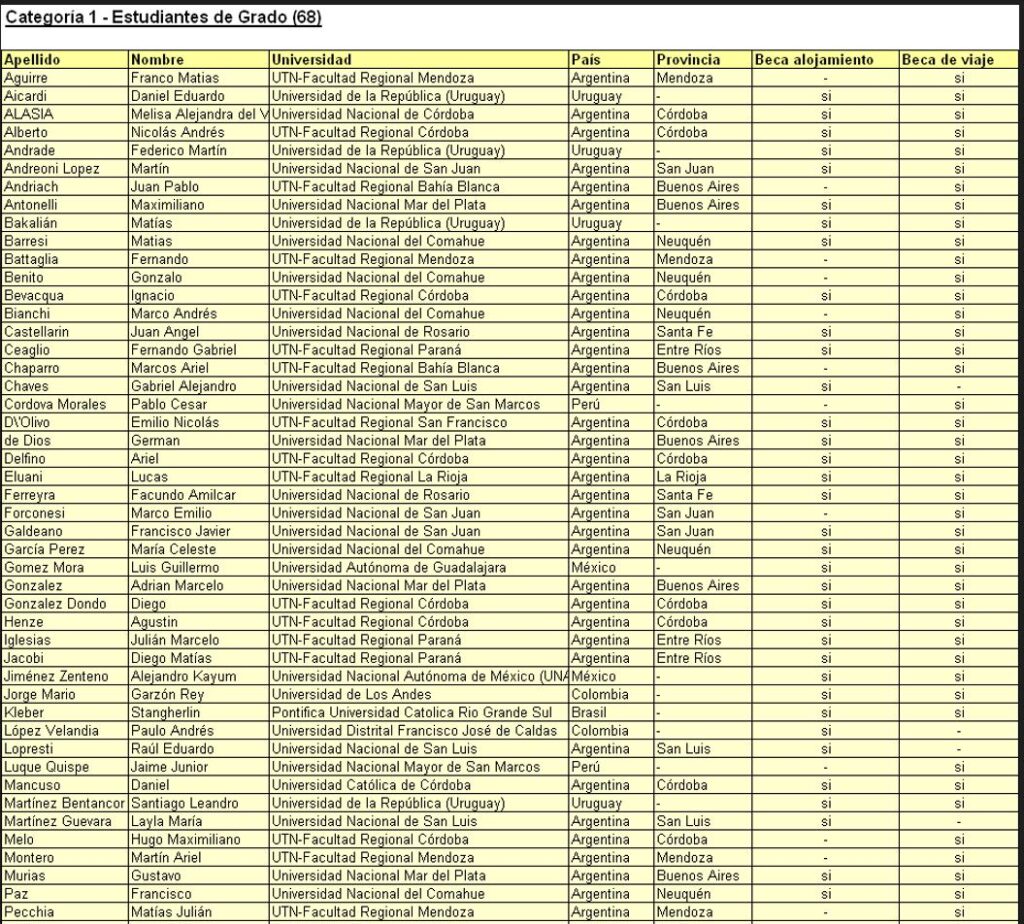

Becas

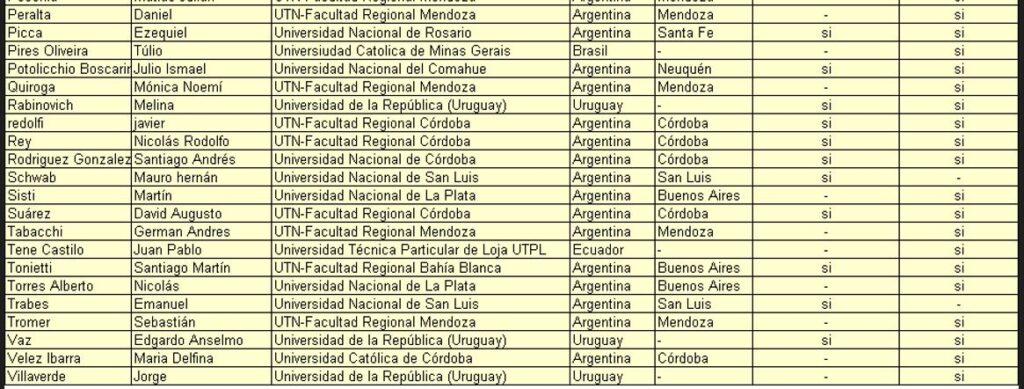

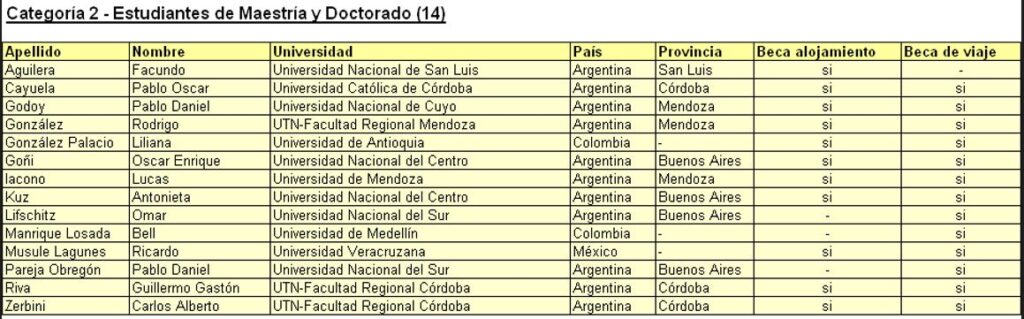

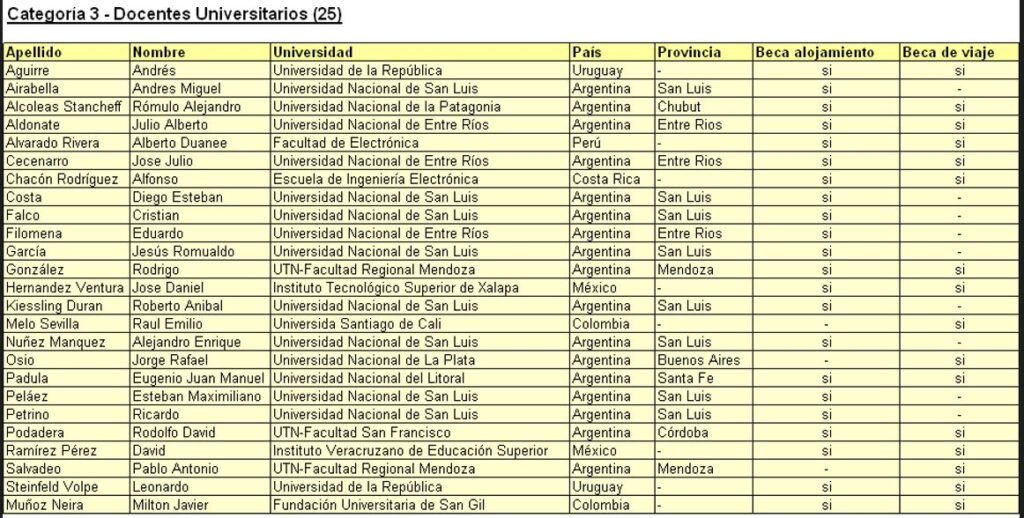

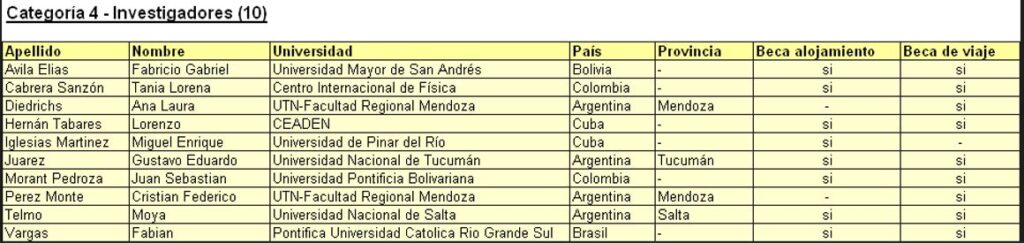

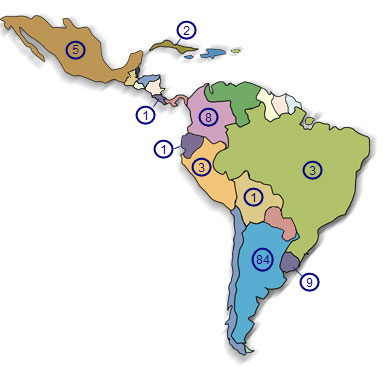

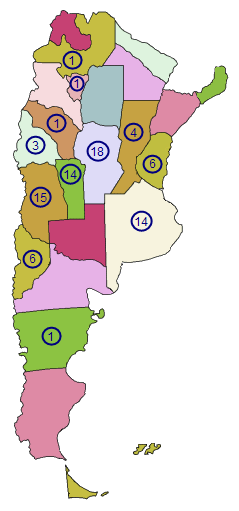

Se otorgaron 117 becas de viaje y alojamiento otorgadas en el SASE 2011. El comité organizador del SASE 2011 informa que se han otorgado 117 becas de viaje y alojamiento a participantes de Argentina y América Latina (ver imágenes ilustrativas) según el listado que se detalla al pie de esta noticia.

– En el caso de las becas de viaje, cada beneficiario deberá presentar su pasaje original y se le reintegrará el importe correspondiente por un valor que en ningún caso podrá superar a la beca de viaje que haya solicitado.

– En el caso de las becas de alojamiento se ha fijado un limite máximo total de $400 (pesos argentinos) por persona para los Estudiantes de Doctorado, Docentes Universitarios e Investigadores, y un límite máximo de $300 para Estudiantes de Grado, ya que se considera que con este monto es posible costear un alojamiento adecuado.

Organizadores Locales

Coordinación general

Ariel Lutenberg, FIUBA

Programa 2011